随着集成电路的发展,芯片的集成度越来越高,但是相应的耐压也逐渐降低,所以很容易遭受EOS、ESD(静电放电)等瞬态能量的破坏。

ESD(静电保护器)作为现在最主要的保护器件之一,对电路和芯片的保护起到了重要作用。

静电保护器,也叫静电管,英文全称Electrostatic Discharge Suppressor,英文缩写ESD。

一、ESD的工作原理

正常情况下,ESD和被保护的电路或者芯片并联,在不动作的时候,阻值很大,在两端电压小于等于保护器件截止电压的时候,漏电流很小(规格书定义值),基本不产生功率损耗,所以不影响电路正常工作。

当ESD两端的电压超过击穿电压的时候(定义的是1mA电流下的电压),ESD被判定击穿导通,从高阻变成了低阻,根据欧姆定律,I=U/R,这个时候流经ESD的电流会瞬间变大,把过压限制在ESD的最大钳位电压以下,从而起到分流限压的效果。

瞬态过压消失后,ESD又恢复成了高阻状态,从而达到重复保护的效果。

二、ESD与TVS的区别

ESD的工作原理和TVS是一致的,甚至某些时候可以直接称呼ESD为TVS,但是之所以把ESD单独作为一个保护器件种类区分开来,自然是有它的原因的。

首先,TVS的目的是为了防护能量相对较强的浪涌,创造之初就是作为电源口的防护器件用来保护电源接口不被浪涌打坏,所以正常情况下TVS对本身的结电容是没什么要求的,一般不会体现容值Cj这个参数。

但是ESD不同,ESD之所以会诞生,正是因为需要满足某些特定的环境下瞬态过压比如静电对产品信号接口的破坏的防护要求,静电的特性根据国际标准IEC61000-4-2可以知道就算是标准里面定义的最高放电等级——接触放电8KV、空气放电15KV的时候电流也才几十安培,而且静电的脉宽时间是纳秒(ns)级别,所以对产品的通流能力要求没那么高。

但是常规的TVS的封装体积又比较大,放在芯片的信号接口做防护显然是不合适的,同时常规的TVS的容值都是几百pF到几个nF,会严重影响高速信号线的传输,所以急需一种器件可以同时满足这几种条件:一、封装小。二、容值低。三、可以满足保护静电最高等级接触放电8KV空气放电15KV的能力。四、可以把瞬态的过压给降下来。

在这种情况下,ESD诞生了,通过大量降低TVS芯片尺寸,来实现降低容值的效果,同时还能实现小封装的要求,并且可以通过静电实验以及实现钳位效果。

在实际的工程应用当中,很多信号端口的信号线不止一条,比如USB、HDMI等都有多条信号线,所以为了方便,市场上推出了多路阵列式防护器件,比如我司的TUSD05L4U,可以同时防护4路信号线,集成到一颗DFN2510-10L封装的器件里面。

但是由于正常电源都是单路的,所以TVS基本上都是单路防护的,常用封装也就只有SOD-123FL、SMA、SMB、SMC。

综上,ESD和TVS的区别如下:

1、ESD主要用来防护静电,TVS主要用来防护浪涌。

2、ESD封装小、且封装形式多样。

3、ESD容值比TVS小。

三、ESD的电路符号和极性

ESD的电路符号和TVS可以画成一样的,因为用的最多的ESD都是硅材质的,电路符号如下:

四、ESD的伏安特性曲线

最早的ESD和TVS一样都是常规的随着经过器件的IP更大,两端的电压值越高的特性,但是随着时代的发展和需求的变化,增加了具有回扫效果的ESD,所以ESD的伏安特性曲线现在也分成常规的和回扫的,回扫ESD又分浅回扫和深回扫。

几种不同特性的ESD都有各自的适用场景。

五、ESD的分类以及优缺点

ESD其实是一种根据功能命名的器件,主要是用来防护静电,但是根据材料来区分的话,又可以分为三大类,三种类型的ESD特性各有差异:

1,硅基材料:也可以叫做TVS型的ESD,或者直接叫TVS。

优点:反应速度快、钳位电压低、封装形式多样、容值范围比较大、不易老化。

另外,TVS型ESD又分为普通型和回扫型,回扫型主要应对在电路无法进行更改但是同时又会因为残压问题导致后端受到干扰时应用,优点是残压低,但是同样存在“栓锁效应”,即当正常工作电压如果大于回扫后的最小电压时,如果电流超出器件维持电流,则会导致ESD持续导通后失效。

2,压敏材料:正常都是氧化锌材质的小封装压敏电阻,也可以直接叫压敏电阻。

优点:反应速度快、防护等级可以做的较高。

缺点:易老化、残压较高、容值较大。

3,高分子聚合物材料:高分子材料做成的具有防静电功能的小封装保护器件。

优点:容值极低(0.05pF)。

缺点:启动电压高(几百伏)、防护等级低、不耐高温。

六、常见ESD封装

ESD根据保护信号线的路数,又可以分为:单路保护ESD、两路保护ESD、四路保护ESD等,所以ESD的封装形式也有各种类型,如下所示:

DFN0603-2L(0201) | DFN1006-2L(0402) | SOD-523(0603) | SOD-323(0805) |

尺寸—— 长:0.6mm 宽:0.3mm 高:0.3mm | 尺寸—— 长:1.0mm 宽:0.6mm 高:0.5mm | 尺寸—— 长:1.2mm 宽:0.8mm 高:0.6mm | 尺寸—— 长:1.7mm 宽:1.2mm 高:0.9mm |

|

|

|

|

DFN1610-2L | DFN2020-3L | DFN2510-10L | SOT-23 |

尺寸—— 长:1.6mm 宽:1.0mm 高:0.5mm | 尺寸—— 长:2.0mm 宽:2.0mm 高:0.6mm | 尺寸—— 长:2.5mm 宽:1.0mm 高:0.6mm | 尺寸—— 长:3.0mm 宽:1.3mm 高:1.0mm |

|

|

|

|

SOT-143 | SOT-23-6L | ||

尺寸—— 长:2.9mm 宽:1.3mm 高:1.0mm | 尺寸—— 长:3.0mm 宽:1.6mm 高:1.3mm | ||

|

| ||

当然,以上是常规封装,随着市场需求变化,也有一些特定接口的保护会需求其它形式的封装,比如SOT-323、SOT-363等,主要是由于PCB小型化无法放进多颗ESD的情况导致的需求,正常情况下,如果PCB允许的情况,封装大引脚大一点有利于电流泄放,可以不用选择的太极限,以免出现其它问题。

七、ESD的关键参数

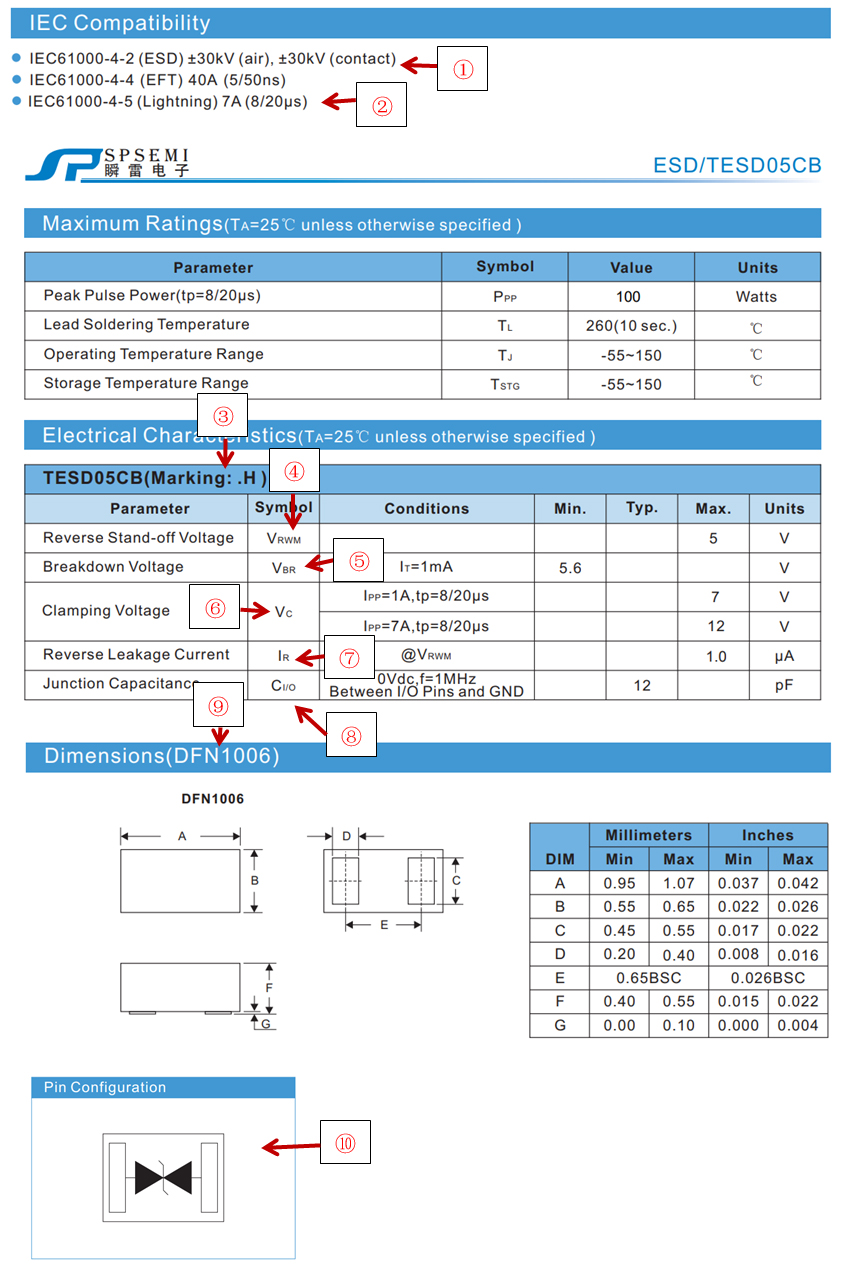

①,静电防护等级:器件可以保护的最大的静电等级。 说明:阻容模组正常是IEC模型150pF、330Ω,放电模式根据静电枪头是否接触EUT分为接触放电和空气放电,根据是测试EUT还是耦合板分为直接放电和间接放电,通常情况下,这里的放电等级是在直接放电的模式下测试的。 |

②,8/20us 波形峰值脉冲电流:器件在8/20us波形下可以承受的最大电流。 备注:之所以没有评估功率,主要是考虑现有器件的特性不是功率越大越好,因为Ppp=IPP*VC,而回扫型ESD的VC很低,所以功率高有可能意味着残压也很高, |

③,丝印:表示产品本体上的印字。 |

④,截止电压(Vrwm,Reverse stand-off voltage):安全工作电压,器件两端电压小于等于截止电压时,器件的漏电流≤规格书定义的漏电流。 说明:所以如果产品工作电压超出器件截止电压,器件两端的漏电流就会变大,最后导致器件性能损伤或者直接导通失效。 |

⑤,击穿电压(VBR,Breakdown voltage):触发电压、动作电压、在器件两端电压大于等于击穿电压时,判定器件被击穿,实际是在规格书定义的测试电流IT(1mA)下对应的电压。 |

⑥,最大钳位电压(VC,Maximum Clamping Voltage):在对应波形(正常情况下是在10/1000us的纯电流波)的IPP的情况下,器件两端的限制电压(也叫残压、钳位电压、保护电压等)。 说明:在不同的电流的情况下,ESD两端的VC会有差异。 |

⑦,反向漏电流(IR,Reverse Leakage):定义在器件两端电压为截止电压Vrwm的时候器件的反向电流。 |

⑧,结电容:器件两端的电容值。 说明:高速信号线对并联在上面的器件的电容值比较敏感,因为会影响电路正常的信号传输。 |

⑨,产品封装:表明产品的封装形式。 |

⑩,极性:只有一颗单向TVS意味着是单向器件,有两颗则是双向,单双向也可以通过I-V特性曲线来进行判断。 |

八、ESD的选型考虑

底层逻辑:在不影响要保护的电路平时正常工作的情况下,还能在异常的过压经过的时候,把电压降下来,达到保护后面的电路或者芯片的目的,同时保护器件本身还不能被打坏。

分析:

1,如何实现在加了ESD后不影响电路正常工作?

——针对电源端口,主要会影响电路正常工作的因素是ESD的两端的电压和漏电流,漏电流大会导致电路损耗增大,对于ESD本身来说,正常不动作之前漏电流是很小的,但是在触发导通之后,器件的反向电流会变大,持续保持这个状态ESD有失效的风险。

所以,针对以上考虑,ESD首先需要考虑截止电压Vrwm的选择,因为截止电压就是针对性的给出的安全电压的建议,如果电路本身的工作电压超出器件的截止电压,那么漏电流就有可能会超出TVS规格书给出的范围,产生安全隐患。

也就是:Udc < Vrwm

——针对信号端口,分为高速信号和低速信号,需要考虑到ESD的结电容,不同的传输速率,对容值要求越高,不同传输速率下建议应用的器件容值如下:

2,怎么实现异常过压经过ESD后,ESD可以有效保护后面的电路或芯片。

——这里主要考虑的是器件两端的残压,但是由于这里的残压是瞬态的,而后端芯片的耐压是常态的,所以还是需要实际测试验证。

如果在PCB不能动的情况下,可以先尝试用几种方法降低器件两端残压:

①,选用残压更低的器件或者回扫型的器件。

②,选用IPP更大的器件。

如果PCB可以更新,可以尝试用以下几种方案降低残压:

①,线路上串联电阻并联电容等退耦器件,因为经典的脉冲持续时间只有纳秒级别,所以瞬间的脉冲尖峰非常高,可以通过增加电阻等退耦的方式吸收尖峰残压。

②,把ESD的地阻抗减少,加快ESD动作时间。

静电的防护除了传导以外,还有耦合的方式,因为ESD频率非常快,所以容易直接和敏 感金属引脚形成电容电流路径,尽量把敏感信号离地物理路径远一点以免产生耦合。

3,ESD自身不能被打坏。

——这个主要是考虑ESD的防静电等级,选择一个比需求的等级高的ESD就可以了。